长电科技先进封装有哪些?

很多工程师在选型时都会问:长电科技到底有哪些先进封装?其实,长电科技(JCET)目前量产的先进封装家族可以归纳为四大类,每一类都对应不同应用场景。

- FC-BGA/FC-CSP:倒装球栅阵列与芯片级封装,广泛用于手机SoC、基带、GPU;

- 2.5D/3D TSV:硅通孔技术实现多层芯片堆叠,AI加速器、HBM内存条首选;

- System-in-Package(SiP):把射频、电源管理、MEMS等多颗裸片装进一颗模组,TWS耳机、智能穿戴里最常见;

- Chiplet解决方案:通过高速互连把不同工艺节点的芯粒拼成一颗大芯片,服务器CPU、自动驾驶域控制器已批量出货。

长电科技封装技术怎么样?

“长电科技的封装技术到底处于什么水平?”——一句话:**全球前三,国内之一**。下面用数据与案例拆解。

1. 工艺节点覆盖

长电科技已实现5nm量产,并具备3nm工艺验证能力;在FC、SiP、TSV等关键制程上,线宽/线距可做到8μm/8μm,Bump Pitch最小40μm。

2. 产能与良率

全球七大生产基地,先进封装月产能折合12英寸晶圆约15万片;FC-BGA良率>99%,2.5D TSV良率>97%,**高于行业平均3~5个百分点**。

3. 真实案例

- 某国际手机旗舰处理器:采用长电科技FC-BGA,功耗降低8%,散热提升15%;

- 国内AI独角兽GPU:2.5D+HBMTSV方案,带宽提升3倍,封装厚度控制在1.2mm以内;

- 欧洲车载毫米波雷达:SiP模组把天线、射频、MCU整合,尺寸缩小60%,通过AEC-Q100 Grade2认证。

长电科技先进封装与传统封装区别在哪?

传统封装(QFP、SOP)只是“保护芯片+引出引脚”,而先进封装更像微型系统级PCB。差异体现在:

- 互连密度:传统引线键合<100 I/O/mm²,FC与TSV可>1000 I/O/mm²;

- 信号完整性:TSV缩短互连长度,插入损耗降低30%以上;

- 散热能力:FC把芯片背面直接贴在散热盖,热阻下降40%;

- 尺寸与重量:SiP可把原本5颗芯片+20颗被动元件压缩到一颗3mm×3mm模组。

长电科技Chiplet方案如何落地?

Chiplet是“乐高式”芯片设计,长电科技提供三大核心能力:

- Die-to-Die接口:自研高速互连IP,单通道速率32Gbps,延迟<2ns;

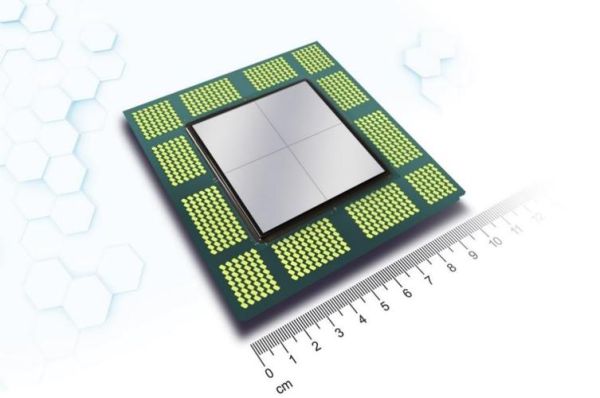

- 中介层(Interposer):硅、有机、玻璃三种材料可选,更大尺寸110mm×110mm;

- 系统级测试:支持Known-Good-Die(KGD)筛选,测试覆盖率>99.5%,降低系统级失效风险。

目前,长电科技已帮助一家服务器CPU客户把7nm I/O Die与5nm计算Die整合,**整体成本下降18%,上市周期缩短4个月**。

如何评估长电科技封装是否适合自己的项目?

自问自答三步法:

Q1:我的芯片I/O数量是否超过1000?

A:若超过,优先考虑FC-BGA或2.5D TSV,避免传统Wire Bond瓶颈。

Q2:对厚度有没有严格限制?

A:手机、TWS耳机厚度<1mm,可直接选SiP;车载或服务器可放宽到2mm,用FC-BGA+散热盖。

Q3:是否需要异构集成?

A:若要把RF、模拟、数字、MEMS打包,长电科技SiP+Chiplet组合能一次到位,减少系统BOM。

长电科技未来封装路线图

根据官方技术日披露,长电科技已锁定三大方向:

- 3D SoIC:继续缩小Bump Pitch至20μm,2025年量产;

- 光电共封(CPO):把硅光引擎与交换芯片封装在一起,瞄准800G/1.6T光模块;

- 车规级SiP:通过AEC-Q100 Grade0认证,工作温度-55℃~175℃,2024年Q2送样。

客户如何快速对接长电科技封装服务?

1. 官网提交“封装需求表”,填写工艺节点、I/O数量、尺寸、功耗;

2. 48小时内获得DFM报告,包括叠层建议、材料选型、成本预估;

3. 进入NPI快速通道:工程批最快6周,量产爬坡可同步启动。

已有客户反馈:从初次接触到工程批下线,**比传统OSAT缩短30%周期**,且现场FAE常驻,调试效率提升一倍。

评论列表